- 您现在的位置:买卖IC网 > Sheet目录1204 > CSIX-PI40-O4-N1 (Lattice Semiconductor Corporation)INTERFACE IP CSIX TO PI40 ORCA 4

�� �

�

Lattice� Semiconductor�

�CSIX-to-PI40� IP� Core� User’s� Guide�

�Parameter� Descriptions�

�The� list� of� parameters� used� for� con?guring� the� CSIX-to-PI40� core� is� listed� below.� The� values� of� these� parameters�

�are� to� be� set� and� must� be� done� prior� to� synthesis� or� functional� veri?cation.�

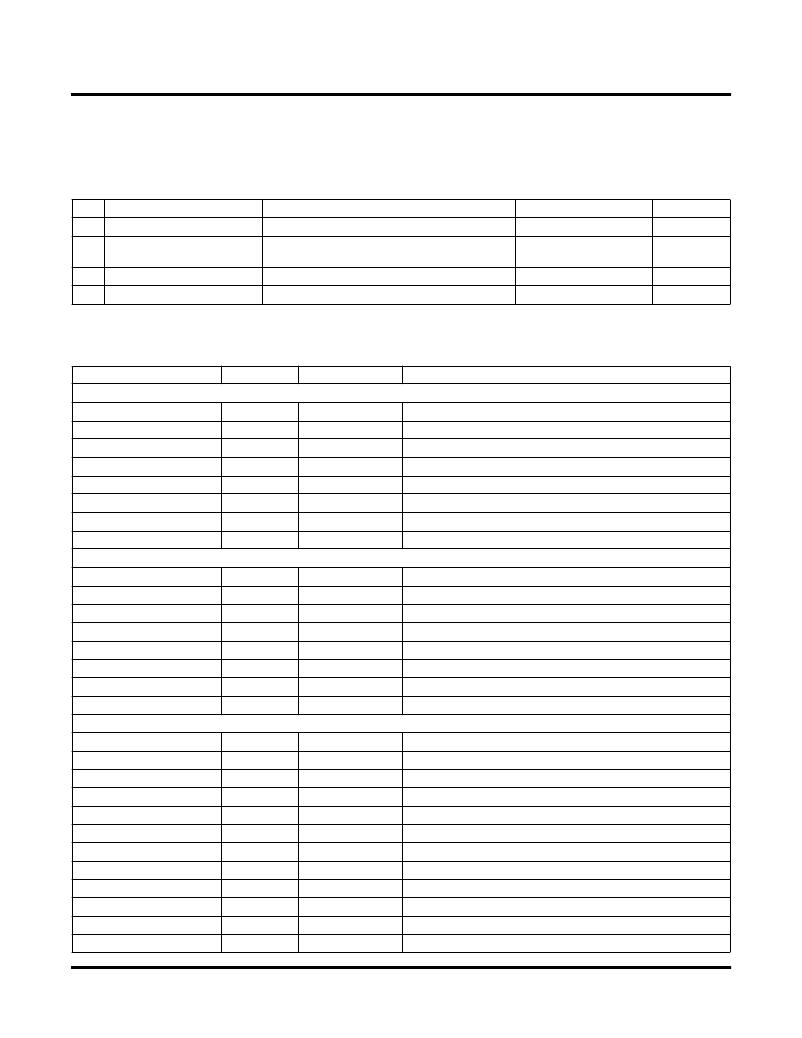

�Table� 1.� User� Con?gurable� Parameters�

�No.�

�1�

�2�

�Parameter�

�NUM_OF_CHANNELS�

�PI40_CELL_SIZE�

�Description�

�Number� of� CSIX� channels�

�PI40� cell� size� and� corresponding� Cframe�

�Choice�

�1� or� 2�

�76,� 84� or� 92� bytes�

�Default�

�1�

�92� bytes�

�MAX_FRAME_PAYLOAD_SIZE� (56,64,72).�

�3�

�4�

�PROTECTION�

�BUFFER_TYPE�

�Support� ability� to� switch� between� two� fabrics.�

�Buffer� type� used� for� external� CSIX� Pins.�

�Yes� or� no�

�LVCMOS� or� HSTL�

�yes�

�LVCMOS�

�Signal� Descriptions�

�Table� 2.� Signal� De?nitions� of� CSIX-to-PI40� Core�

�Signal� Name� 1�

�Direction�

�Width� (Bits)�

�Description�

�CSIX� Interface� (FPGA� Primary� I/Os)�

�c6_data_in_N_ext[31:0]�

�c6_parity_in_N_ext�

�c6_sof_in_N_ext�

�c6_clk_in_N_ext�

�c6_data_out_N_ext[31:0]�

�c6_parity_out_N_ext�

�c6_sof_out_N_ext�

�c6_clk_out_N_ext�

�Input�

�Input�

�Input�

�Input�

�Output�

�Output�

�Output�

�Output�

�32�

�1�

�1�

�1�

�32�

�1�

�1�

�1�

�Inbound� Data�

�Inbound� Parity� (Odd)�

�Inbound� Start� of� Frame�

�Inbound� Clock� (100MHz)�

�Outbound� Data�

�Outbound� Parity� (Odd)�

�Outbound� Start� of� Frame�

�Outbound� Clock� (100MHz)�

�SERDES� Interface� (FPGA� Primary� I/Os)�

�hdinna[a:d]�

�hdinpa[a:d]�

�hdoutna[a:d]�

�hdoutpa[a:d]�

�hdinnb[a:d]�

�hdinpb[a:d]�

�hdoutnb[a:d]�

�hdoutpb[a:d]�

�Input�

�Input�

�Output�

�Output�

�Input�

�Input�

�Output�

�Output�

�1�

�1�

�1�

�1�

�1�

�1�

�1�

�1�

�SERDES� receive� data� input�

�SERDES� receive� data� input�

�SERDES� receive� data� output�

�SERDES� receive� data� output�

�SERDES� receive� data� input�

�SERDES� receive� data� input�

�SERDES� receive� data� output�

�SERDES� receive� data� output�

�Register� Interface� (FPGA� Primary� I/Os,� Do� Not� Replicate)�

�mpi_clk�

�mpi_addr[14:31]�

�mpi_rdwr_n�

�mpi_strbn�

�mpi_tsz[0:1]�

�mpi_burst�

�mpi_bdip�

�cs0n�

�cs1�

�mpi_ta�

�mpi_retry�

�mpi_tea�

�Input�

�Input�

�Input�

�Input�

�Input�

�Input�

�Input�

�Input�

�Input�

�Output�

�Output�

�Output�

�1�

�18�

�1�

�1�

�2�

�1�

�1�

�1�

�1�

�1�

�1�

�1�

�Clock� (50� MHz)�

�Address� bits�

�Write� High� /� Read� Low�

�Data� transfer� strobe�

�Data� transfer� size�

�Active� low� burst� transfer� indicator�

�Active� low� for� processor� request� of� second� beat�

�Active� low� chip� select�

�Active� high� chip� select�

�Active� low� acknowledge� to� processor�

�Active� low� retry� request� to� processor�

�Active� low� indicator� to� processor� of� internal� bus� error�

�4�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

CT0805S14BAUTOG

VARISTOR 14VRMS 0805 SMD AUTO

CT1206K17G

VARISTOR 17VRMS 1206 SMD

CTB-B-B-15

CIRCUIT BREAKER ROCKER 15A SP BK

CU3225K17AUTOG2

VARISTOR AUTO 17VRMS 3225 SMD

CU3225K250G2K1

VARISTOR STD 250VRMS 3225 SMD

CV10-RP-M-0

CONN JACK STR COAXIAL SMD

CVM50XM

MEMBER MOD PIC12C508/PIC12C509

CVM67XM

MEMBER MODULE PIC12C671/672

相关代理商/技术参数

CSJ-100

制造商:GREENLEE TOOL CO 功能描述:Digital Open Jaw Clampmeter 制造商:Greenlee Textron Inc 功能描述:CLAMPMETER

CSJ-23

功能描述:EXTRACTION TOOL FOR SCS RoHS:否 类别:工具 >> 插入,抽取 系列:* 标准包装:1 系列:* 其它名称:0011-03-00080011-03-0008-E00110300080011030008-E11-03-0008-E1103000811030008-EQ4729393AT0980176A

CSJ32C1

制造商:未知厂家 制造商全称:未知厂家 功能描述:HC-49/US SMD Microprocessor Crystals

CSJ32C3

制造商:未知厂家 制造商全称:未知厂家 功能描述:HC-49/US SMD Microprocessor Crystals

CSJ32C5

制造商:未知厂家 制造商全称:未知厂家 功能描述:HC-49/US SMD Microprocessor Crystals

CSJ32E1

制造商:未知厂家 制造商全称:未知厂家 功能描述:HC-49/US SMD Microprocessor Crystals

CSJ32E3

制造商:未知厂家 制造商全称:未知厂家 功能描述:HC-49/US SMD Microprocessor Crystals

CSJ32E5

制造商:未知厂家 制造商全称:未知厂家 功能描述:HC-49/US SMD Microprocessor Crystals